## Temperature influence on strained nMuGFETs after proton radiation

C. Bordallo<sup>1</sup>, P.G.D. Agopian<sup>1,2</sup>, J.A. Martino<sup>2</sup>,

E. Simoen<sup>3</sup> and C. Claey<sup>3,4</sup>

<sup>1</sup>Centro Universitário da FEI, SBC, Brazil

<sup>2</sup>LSI/ PSI/USP - University of São Paulo, SP, Brazil

<sup>3</sup>imec, Leuven, Belgium

<sup>4</sup>E.E. Dept., KU Leuven, Leuven, Belgium

The multiple-gate devices (MuGFETs) are an alternative to minimize short channel effects, presenting better scalability than single gate devices, and also have higher radiation hardness (1). In spite of these advantages, MuGFETs present a smaller effective electron mobility due to the lateral conduction in the (110) plane. Stress engineering has been used to improve the electron mobility (2). In this work the influence of high temperatures on highly stressed devices is studied before and after proton irradiation.

The used devices were fabricated at imec, Belgium. Their characteristics are: channel length of 150nm, fin height of 65nm, buried oxide of 150nm and fin width ( $W_{FIN}$ ) ranging between 40 and 870 nm. The gate electrode is composed by 100nm of polysilicon over 5 nm of TiN and the gate dielectric consists of 2.3nm HfSiON on 1 nm  $\text{SiO}_2$ . All devices have source and drain contacts with Selective Epitaxial Growth (SEG) to reduce series resistance. Additional process information can be found in (3). The 60 MeV proton irradiations have been performed up to a fluence of  $10^{12} \text{ p/cm}^2$  at the Cyclone facility in Louvain-la-Neuve (Belgium). The stressed devices combine the biaxial stress of a sSOI wafer and the tensile uniaxial stress (Contact Etch Stop Layer -CESL) in the same device. As the stresses have an additive effect, it results in a high effectiveness of the stress.

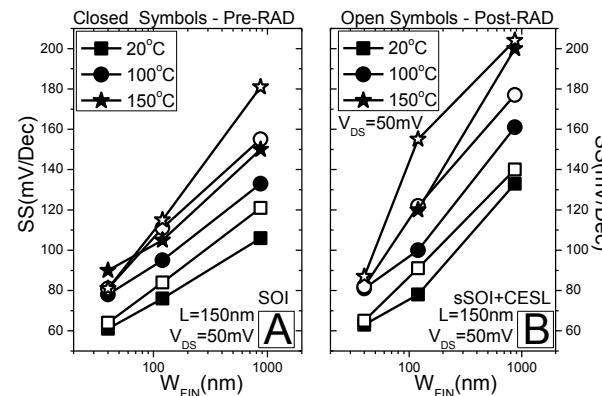

The subthreshold swing (SS) is a parameter that can describe the switching performance of a device and the analysis of this parameter is shown in figure 1, for unstressed devices (1A) and for stressed devices (1B). Wider devices present higher SS because these devices have less sidewall gate to channel coupling leading to short channel effects (SCE). Narrow devices have more radiation hardness due to the small area and higher coupling between gates that keeps SS almost constant. However, for wider devices the radiation causes a significant increase of SS, due to the charges induced in the buried oxide that promote a reduction of the back interface threshold voltage ( $V_{th2}$ ) resulting in a higher leakage current at the back interface.

When the temperature and the high effective stress are taken into account, the SS degradation is even more significant as both factors (stress and temperature) also contribute to the bandgap narrowing (4) and consequently leads to a  $V_{th2}$  reduction and high back conduction.

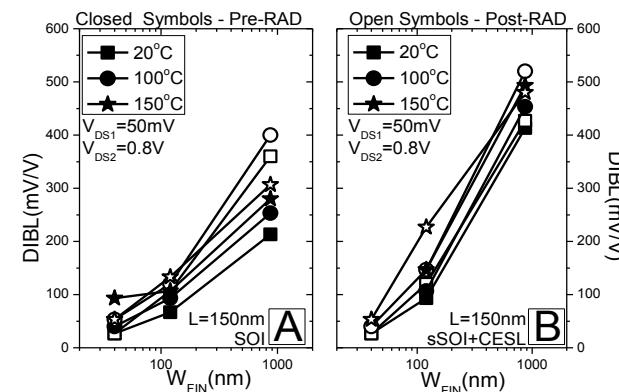

The Drain Induced Barrier Lowering (DIBL) (5) dependence on radiation, temperature and fin width for unstressed devices and stressed ones is shown in figures 2A and 2B, respectively. From figure 2A it is possible to observe that as  $W_{FIN}$  increases the DIBL becomes higher due to the lower coupling between gates and the high SCE susceptibility. As the temperature increases a degradation in DIBL for wider fins is observed. It occurs because wider fins present less coupling between gates and when the temperature increases the vertical electrical field at the Si surface reduces, that in turn, permits a higher influence of the drain electric field on the channel region. Subjecting these devices to proton radiation, the DIBL is degraded even more. This degradation is due to the increase of the oxide and interface trap charges and consequently due to the high backside conduction influence (6). On the other hand, when the stress is considered (figure 2B), the generated number of defects and the bandgap narrowing are enough to strongly degrade the DIBL (7). Comparing all the influences on DIBL, the stress shows to be more harmful than radiation and temperature effects.

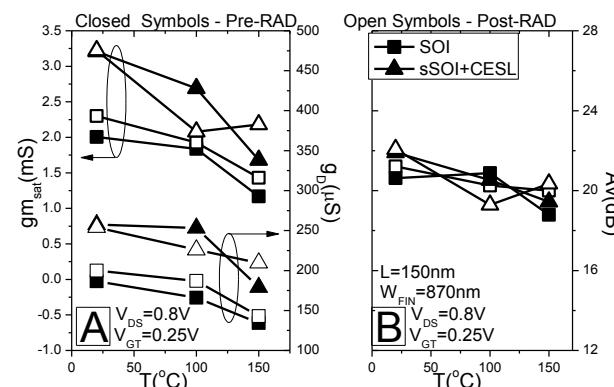

The intrinsic voltage gain ( $A_V$ ) was analyzed through the relationship between the transconductance in the saturation region ( $gm_{sat}$ ) and the output conductance ( $g_D$ ),  $A_V = gm_{sat}/g_D$ .

Figure 3 presents the  $gm_{sat}$  and  $g_D$  (A), and  $A_V$  (B) as a function of temperature for strained and unstrained devices. The increase of the temperature causes a  $g_D$  decrease, due to the reduction of the depletion region caused by the decrease of the electric field.

However, increasing temperature results in a more intensive  $gm_{sat}$  reduction due to mobility degradation, causing a reduction of  $A_V$ . The stress, in turns, causes an increase in the  $g_D$  and an improvement in the  $gm_{sat}$  due to a high enhancement on electron mobility, but since  $A_V$  is the ratio between  $gm_{sat}$  and  $g_D$ , the higher value of  $gm_{sat}$  is compensated by the  $g_D$  increase, resulting in an almost constant  $A_V$ .

Considering all these influences on the  $A_V$  behavior, as can be seen in Fig. 3, it is possible to notice that the influence of temperature is more important than the influence of radiation and stress.

Radiation and stress that strongly degrade digital characteristics have less influence on analog characteristics. On the other hand, the temperature makes the analog and digital performance of the devices worse.

Figure 1: SS as a function of  $W_{FIN}$  at 20°C, 100°C and 150°C for (A) strained and (B) unstrained devices before and after proton irradiation.

Figure 2: DIBL as a function of  $W_{FIN}$  at 20°C, 100°C and 150°C for (A) strained and (B) unstrained devices before and after proton irradiation.

Figure 3: Transconductance ( $gm_{sat}$ ) and output conductance ( $g_D$ ) (A), and intrinsic gain ( $A_V$ ) (B) in function of temperature for strained and unstrained devices before and after proton irradiation.

## References

1. J.P. Colinge, FinFET and Other Multigate Trans., Springer, (2007)

2. C. Claey<sup>3</sup> et al., Solid-State Electronics, 52, 1115 (2008).

3. N. Collaert et al., VLSI Symp. Dig. Tech. Papers, 52 (2006).

4. J. Chen et al., IEEE Electron Device Lett., vol. EDL-8, 515 (1987).

5. M. Jamal Deen et al., IEEE Trans. Electron Devices, vol.39, 908 (1992).

6. P. Agopian et al., IEEE Trans. Nucl. Sci., vol. 59, 707 (2012).

7. S.D. Santos et al., Electrochem. Soc. Trans., vol. 23, no.1, 591 (2009).