## Characterization of the Descum Process for Various Silicon Substrates

C. Tiwari<sup>1</sup>, Y. S. Lim<sup>1</sup>, R. Fulton<sup>1</sup>, J. Srinivasan<sup>1</sup>, M. Gisinger<sup>1</sup>, P. M. Flynn<sup>2</sup>, L. H. Mak<sup>2</sup> Micron Technology, Inc. 9600 Godwin Drive, Manassas, VA 20110<sup>1</sup> 8000 S. Federal Way, Boise, ID 83707<sup>2</sup>

The descum process is used to remove organic residue remaining after photolithography steps in the integrated circuit manufacturing process [1] [2] [3]. The descum process removes photo resist residue and provides a clean surface for subsequent process steps such as wet etch, implant, and dry etch [4].

Descum is a low-temperature, O<sub>2</sub>-based plasma process with the objective of removing a few hundred angstroms of resist [5] [6]. This process is controlled by monitoring the resist loss on blanket wafers. Multiple process parameters have a major impact on resist loss, including process temperature, plasma power, and gas flow rates. These parameters are controlled by the manufacturing recipe and descum equipment settings.

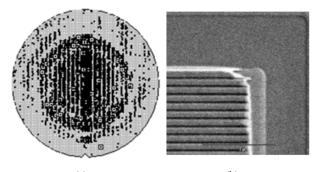

In addition to recipe and equipment parameters, this paper demonstrates that the descum process is highly influenced by silicon substrate doping. The motivation for this study was the discovery that the descum process has a negative impact on wafer patterns. The descum process has removed more resist than was modeled in the manufacturing process flow, based on previous applications of the descum process. This exposed some unintended areas of the wafer to the subsequent dry etch process, damaging the wafer pattern (Fig. 1).

(a) (b) Fig. 1. Negative effect of descum process shown by (a) wafer inspection map; (b) SEM image of damaged pattern.

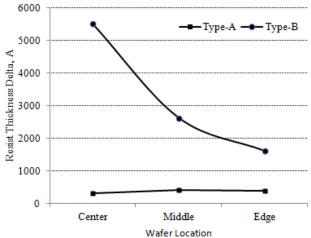

Tests were conducted to understand and characterize the descum process. Fig. 2 shows the resist loss from a 44s descum process for two different types of silicon substrates. Type A wafers were lightly B-doped, while type-B wafers were highly B-doped. The resist loss for type-A wafers was ~400Å spread uniformly across the wafer, while resist loss for type-B wafers was ~5500Å at the center and ~1500Å at the edge.

This paper presents a possible mechanism for the high resist loss and poor uniformity in type-B wafers, as well as the characterization of various factors.

## References:

1. P. Garnier, G. Briend, D. Jeanjean, and M. May, *ECS Transactions*, 41 (5), p. 253-256, 2011

2. L. A. Keser, R. Bajaj, and T. Fang, *IEEE*

*Transactions on Advanced Packaging*, 31 (1), p. 1-6, 2000 3. C. W. Ju, and S. S. Park, *Journal of the Korean*

3. C. W. Ju, and S. S. Park, *Journal of the Korean Physical Society*, 39, p. S147-S150, 2001

P. Garnier, T. Vessa, A. S. Larrea, B. Pernet, Y. Gomez, D. Barge, A. Torres, B. Travel, C. Hederson, and D. Levy, *ECS Transactions*, 11 (2), p. 257-264, 2007

D. Nyyssonen, *SPIE Proceedings*, 480, p. 66, 1984

6. W. G. Oldham, S. N. Nandgaonkar, A. R. Neureuther, and M. O'Toole, *IEEE Transactions on Electron Devices*, ED-26 (4), p. 717-722, 1979