Electrical Properties and Charge Transport in the Pd/Al<sub>2</sub>O<sub>3</sub>/InGaAs MOS Structure

Y.Y. Gomeniuk<sup>1</sup>, Y.V. Gomeniuk<sup>1</sup>, A.N. Nazarov<sup>1</sup>,

S. Monaghan<sup>2</sup>, K. Cherkaoui<sup>2</sup>, É. O'Connor<sup>2</sup>,

I. Povey<sup>2</sup>, V. Djara<sup>2</sup> and P.K. Hurley<sup>2</sup>

<sup>1</sup> ISP NAS of Ukraine, 03028 Kiev, Ukraine

<sup>2</sup>Tyndall NI, Lee Maltings, Prospect Row, Cork, Ireland

High mobility channel material such as high Incontent InGaAs is considered as a potential candidate for replacing strained Si in future CMOS devices [1]. The use of high- $\kappa$  dielectric materials in conjunction with the III-V channel region is required to realise MOSFET structures. We present results of electrical characterization and the determination of the dominant transport mechanism in the  $Pd/Al_2O_3/In_{0.53}Ga_{0.47}As/InP$  MOS system. The high- $\kappa$ Al2O3 oxide layer of the MOS capacitor structure was formed by an ALD process with nominal physical thickness  $t_{ox}$  of 5, 10, 15 and 20 nm. Prior to gate oxide deposition the In<sub>0.53</sub>Ga<sub>0.47</sub>As surface was passivated by an immersion in 10% (NH<sub>4</sub>)<sub>2</sub>S solution at room temperature for 20 min. The samples received no post-metallization annealing treatment. Samples with both n(S)- and p(Zn)type doped  $(4x10^{17} \text{cm}^{-3})$   $In_{0.53}Ga_{0.47}As$  epitaxial layers were characterized by capacitance-voltage (C-V), currentvoltage (I-V) measurements over the temperature range of 100 - 300 K.

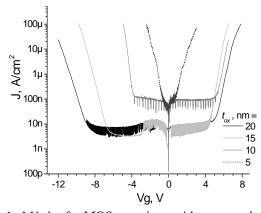

Fig. 1 presents current density (J) vs. gate bias plots for p-MOS structures with different  $Al_2O_3$  thicknesses. The similarity of the J-V curves for both types of the substrates (not shown here) and the general shape of the characteristics are consistent with a current transport mechanism governed by electron tunneling through the triangular potential barrier at the metal-dielectric or semiconductor-dielectric interface. In this case, the current can be described by Fowler-Nordheim (FN) tunneling [2]. The potential barrier  $\varphi_B$  responsible for the carrier transport can be found from the slope of FN plot ( $\ln(J/E^2)$  vs. 1/E) [3].

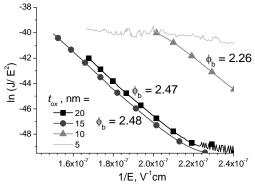

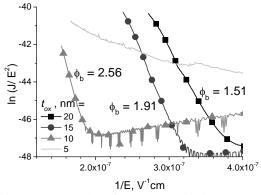

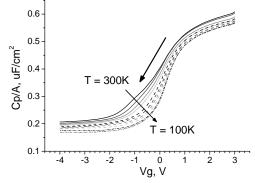

FN plots of the p-type MOS capacitor are shown in Figs. 2-3. The samples with  $t_{ox}$ = 5 nm do not show a well formed barrier at the interfaces possibly due to the dominating of direct tunneling transport mechanism. For the case of electron tunneling from the metal electrode (Fig. 2), the barrier height is the same for the 10, 15 and 20 nm thick dielectric and  $\varphi_B$  equals to 2.40±0.10 eV. For the electron tunneling from the semiconductor (Fig. 3), 10 nm thick dielectric gives the conduction-band energy offset at the Al<sub>2</sub>O<sub>3</sub>/InGaAs interface  $\varphi_B$ =2.50±0.06 eV, which is in a good agreement with the results reported in [4, 5]. From Fig. 3 it is evident that the barrier heights  $(\varphi_{\rm B})$  exhibit an apparent reduction with increasing film thickness. This could be explained by formation of a transition layer in the Al<sub>2</sub>O<sub>3</sub> film due to increased time of dielectric deposition. Also previous analysis has demonstrated that Al<sub>2</sub>O<sub>3</sub> deposited by ALD In<sub>0.53</sub>Ga<sub>0.47</sub>As surfaces exhibits a fixed positive charge distributed throughout the oxide [6]. This positive charge would modify the barrier at the injecting interface resulting in an apparent reduction in the barrier height with increasing oxide thickness. C-V response (see Fig. 4) was recorded after each J-V sweep at the same temperature conditions. It was found that no degradation and non-reversible charge trapping in the dielectric occurred.

## REFERENCES

- 1. J. A. del Alamo, Nature, 479, P.317 (2011).

- 2. R. H. Fowler and L. W. Nordheim, Proc. R. Soc. London,

- Ser. A 119, P.173 (1928).

- M. L. Huang, Y. C. Chang, C. H. Chang et. al., Appl. Phys. Lett. 89, 012903 (2006).

- N. V. Nguyen, M. Xu, O. A. Kirillov, P. D. Ye et al., Appl. Phys. Lett. 96, 052107 (2010).

- J. Ahn, I. Geppert, M. Gunji, M. Holland, I. Thayne et al., Appl. Phys. Lett. 99, 232902 (2011).

- R. D. Long, B. Shin, S. Monaghan, K. Cherkaoui, J. Cagnon, S. Stemmer, P. C. McIntyre, and P. K. Hurley, Journal of The Electrochemical Society, 158 (5) G103-G107 (2011)

Fig. 1. J-V plot for MOS capacitors with p-type substrate.

Fig. 2. The FN plot of *J-V* characteristic ( $V_{\rm g}$  <0) of Pd/Al<sub>2</sub>O<sub>3</sub>/p-In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP structure.

Fig. 3. The FN plot of J-V characteristic ( $V_g$ >0) of Pd/Al<sub>2</sub>O<sub>3</sub>/p- In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP structure.

Fig. 4. 300kHz C-V response of n-MOS capacitor with  $t_{ox}$ =10 nm measured at temperature range of 100 – 300 K.