## Effects of N-rich TiN Capping Layer on Reliability in 20nm Gate-Last High-k/Metal Gate MOSFETs

K.D Bae<sup>a,b</sup>, K.T Lee<sup>a</sup>, H.C Sagong<sup>a</sup>, M.H Choe<sup>a</sup>, H.W Lee<sup>a</sup>, S.E Kim<sup>a</sup>, K.S Kim<sup>b</sup>, J.K Park<sup>a</sup>, S.W Pae<sup>a</sup> and J.W Park<sup>a,\*</sup>

## <sup>a</sup> System LSI Division, Samsung Electronics Co. <sup>b</sup> Samsung Semiconductor Institute of Technology, Korea <sup>a,b</sup> San #24 Nongseo-Dong Giheung-Gu, Yongin-City, Gyeonggi-Do, Korea 446-711

One of the major challenges for the gate-first approach in high-k/metal-gate (HK/MG) transistor fabrication is finding the gate stacks that can survive high temperature annealing (typically over a thousand degrees, °C) and compatible with strain techniques. As transistor size scales down, it becomes hard to find the metals which can endure 1000°C or the high annealing temperature without the metal work function shift that causes performance degradation. Therefore, a gate-last technology where high temperature process has been decoupled from the metal gate processing has been introduced [1]. However, reliability concern is becoming severe, since gate stack can't suffer enough thermal treatment [2].

In this paper, time-dependent dielectric breakdown (TDDB) and bias temperature instability (BTI) of transistors fabricated in 20nm HK/MG gate-last technology are studied with focus on nitrogen enrichment inside the HK/MG stack and its reliability effects.

## **Experimental results and Discussions**

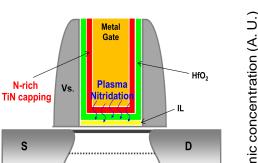

Nitridation in HK to reduce oxygen vacancy is one of candidate methods for improving reliability in HK/MG technology [3]. However, to prevent N<sub>2</sub>-induced defect generation leading to extra NBTI degradation, it is desirable that nitrogen should be concentrated in the bulk HfO<sub>2</sub> while interface layer (IL) is nearly nitrogen free. To attain such stack, deposition of N-rich TiN capping layer versus plasma nitridation (PN) was used as N<sub>2</sub> curing methods are compared in this study (in Fig.1). N-rich TiN deposition

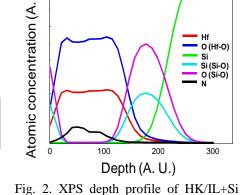

hardly affects the IL because the nitrogen is mostly contained within TiN capping layer. From the X-ray photoelectron spectroscopy (XPS) depth profile (in Fig. 2), the N-rich TiN capping layer sample shows the high nitrogen concentration in the high-k layer but the concentration is low in the IL. The samples fabricated with N-rich TiN capping layer shows negligible difference in gate leakage current compared to the reference (no nitridation) sample while PN sample shows a noticeable increase (shown in Fig. 3) at the given Tinv thicknesses. As indicated above, the sample by PN is supposed to have more defects, resulting in the more gate leakage, due to N injected into IL. On the other hand, N-rich TiN capping layer itself only affects the gate stack with no influence on the IL. Hence, there is no difference of oxide defects and gate leakage current in this study.

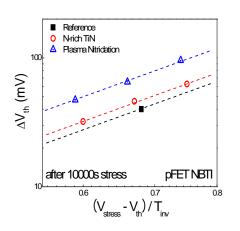

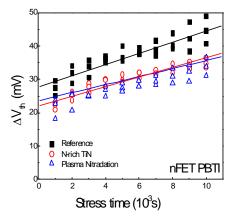

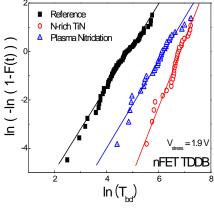

Fig. 4 shows that NBTI on the sample with N-rich TiN capping layer has a slight increase in  $V_{th}$  shift( $\Delta V_{th}$ ) compared to the reference sample; however, it can still surpass 10yr lifetime reliability goal. The PN sample has >2x higher degradation than the reference. We speculate that the plasma-enhanced nitrogen results in more defects on IL due to plasma damage. In case of PBTI (shown in Fig.5),  $\Delta V_{th}$  for the N-rich TiN capping layer and PN samples showed large reduction compared to the reference. It is attributed to the nitrogen passivation of defects (known as Oxygen vancancies) in the high-k bulk layer. Fig. 6 shows that TDDB characteristics of the nFET regardless of N-rich TiN capping layer and PN have also more improved over the reference. However, PN technique has limitations to simultaneously meet TDDB and BTI. In conclusion, Nrich TiN capping layer can be optimized to meet both BTI/TDDB reliability requirements without increase in the gate leakage current.

## Reference

D. Hisamoto, et al., *IEEE TED*, vol. 47, no. 12, 2000

Y. -L Yang, et al., *IEEE EDL*, vol. 33, no. 8, 2012.

C. Choi, et al., in *VLSI Symp. Tech. Dig.*, 2004.

Fig. 1. Schematic diagram of 20nm gatelast HK/MG MOSFETs with N-rich TiN capping or plasma nitridation.

Fig. 4. A slight difference between the sample with N-rich TiN capping layer and the reference.

Fig. 5. N-rich TiN capping layer decreases  $\Delta V_{th}$  significantly due to nitrogen passivation.

Fig. 3. Comparison of gate current density shows that N-rich TiN capping layer induces no significant difference compared to the reference.

Fig. 6. Comparison of TDDB characteristics between N-rich TiN capping layer and PN method.